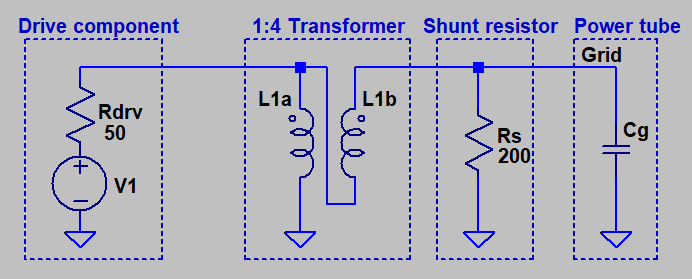

図1 対象回路構成

| 1.まえがき | 2.真空管GKアンプの入力回路 | 3.抵抗負荷への並列容量の影響 | 4.色々な補償回路の方式 | 5.参考資料 |

| 図1 対象回路構成 |

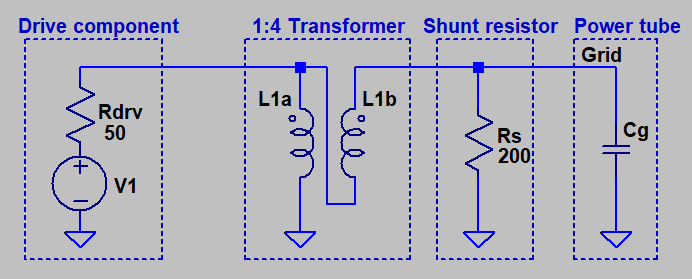

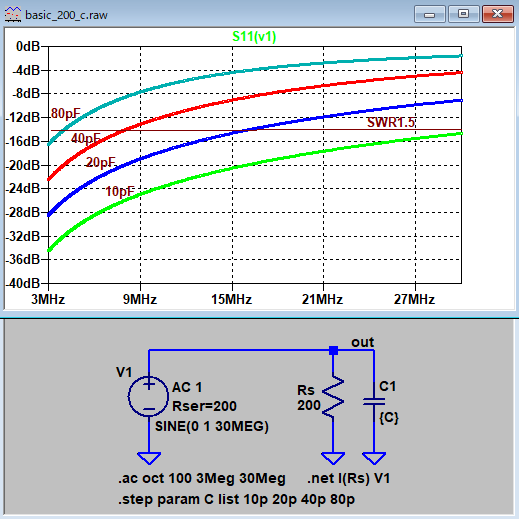

| 図2 信号源インピーダンス200オーム/負荷抵抗200オーム | 図3 信号源インピーダンス50オーム/負荷抵抗50オーム | ||

|

|

|

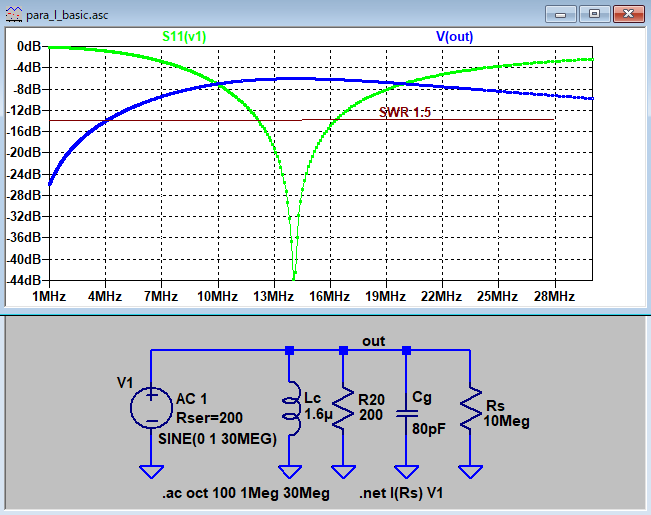

| 図4 並列インダクタンスによる補償 R20 : シャント抵抗 Cg : 電極間容量 Lc : 補償インダクタンス Lc、Cgの共振周波数を目的周波数範囲の中央に採るよう設計する |

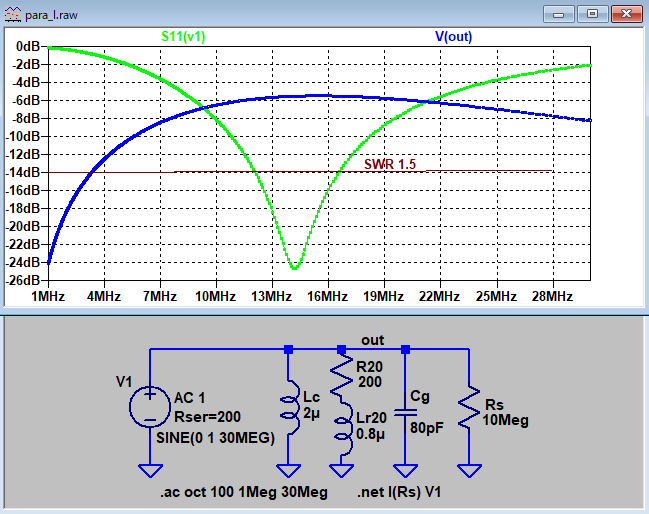

| 図5 並列インダクタンスによる補償 (シャント抵抗寄生インダクタも利用) R20 : シャント抵抗 Lr20 : シャント抵抗の寄生インダクタンス Cg : 電極間容量 Lc : 補償インダクタンス Lc、Lr20、Cgの共振周波数を目的周波数範囲の中央に採るよう設計する |

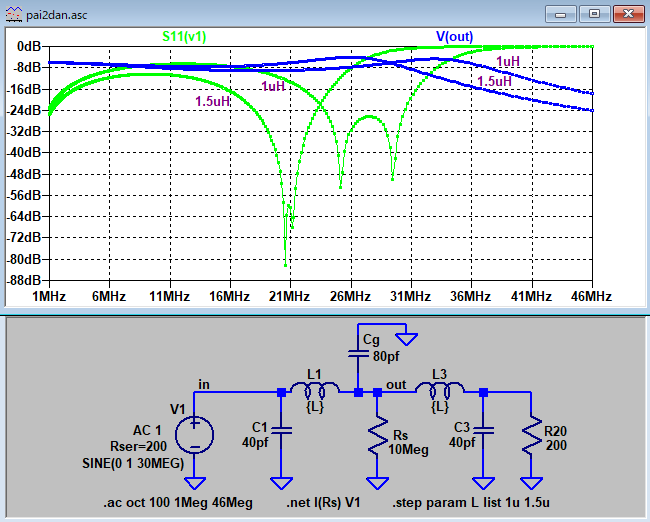

| 図6 パイ型2段 2C点利用 R20 : シャント抵抗 Cg : 電極間容量 L1、L3 : パイ型フィルタ直列インダクタ C1、C3 : パイ型フィルタ並列キャパシタ (=Cg/2) フィルタとしての設計をC1、C3の値ありきで行う 周波数範囲を広げようとコーナ周波数を高めると S11は目減り |

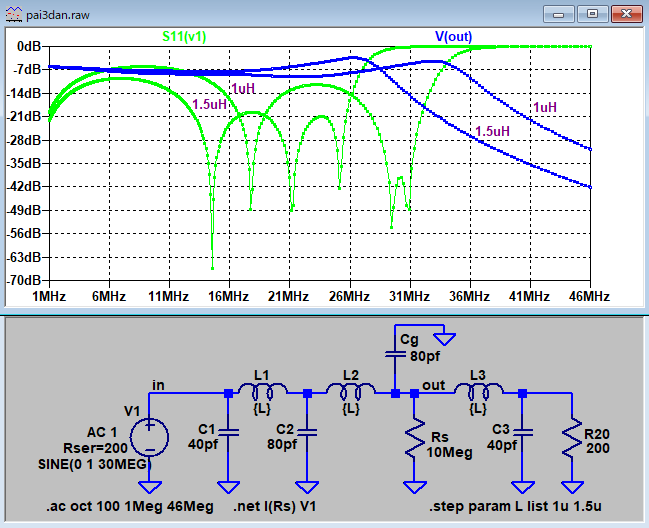

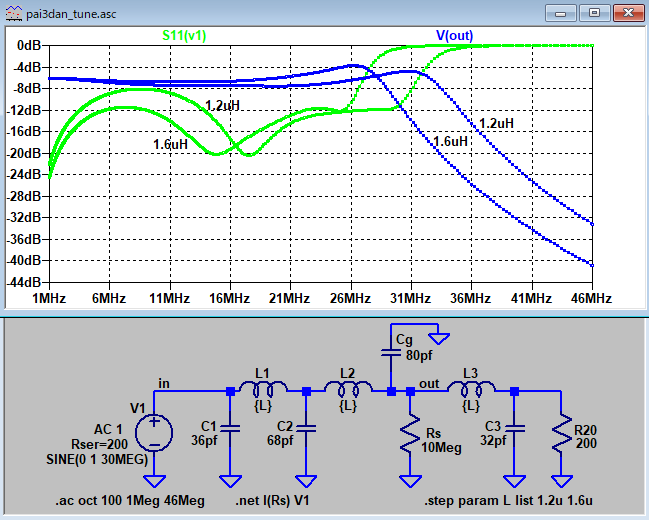

| 図7 パイ型3段 2C点利用 R20 : シャント抵抗 Cg : 電極間容量 L1、L2、L3 : パイ型フィルタ直列インダクタ C1、C3 : パイ型フィルタ並列キャパシタ (=Cg/2) C2 : パイ型フィルタ並列キャパシタ (=Cg) フィルタとしての設計をC1、C2、C3の値ありきで行う 周波数範囲を広げようとコーナ周波数を高めると S11は目減り |

| 図8 パイ型3段 2C点利用(S11重視調整) 図7の状態からS11重視で各素子定数を調整 L1=L2=L3 の条件を外すと改善も出来得るが調整は複雑化 |

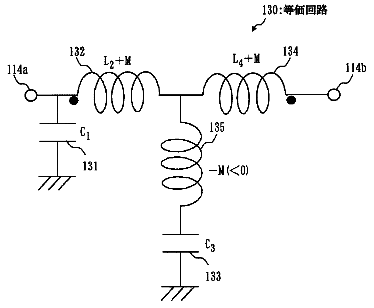

| 図9 当該特許回路 端子114a:入力端、114b:出力端 コイル135、コンデンサ133 :直列共振により減衰極を形成 コイル132、134、135は結合を有する |

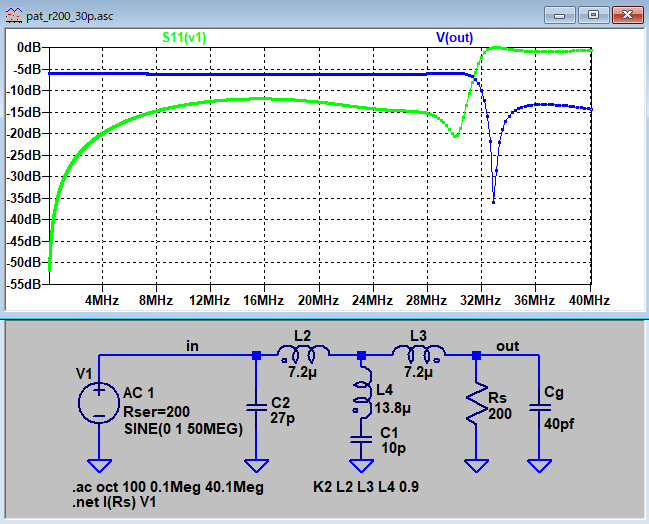

| 図10 並列キャパシタンス 40PF 0.1から30MHzの範囲で S11、最低でも−12dBは得られる |

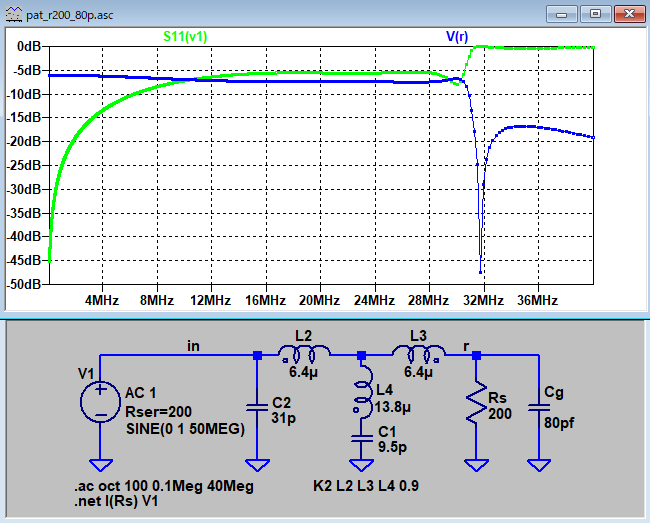

| 図11 並列キャパシタンス 80PF 0.1から30MHzの範囲で S11、最低でも−5dBは得られる |